# Ge2Sb2Te5 layer used as solid electrolyte in conductive-bridge memory devices fabricated on flexible substrate

D. Deleruyelle, Magali Putero, T. Ouled-Khachroum, Marc Bocquet, M.V. Coulet, Xavier Boddaert, C. Calmes, Christophe Muller

#### ▶ To cite this version:

D. Deleruyelle, Magali Putero, T. Ouled-Khachroum, Marc Bocquet, M.V. Coulet, et al.. Ge2Sb2Te5 layer used as solid electrolyte in conductive-bridge memory devices fabricated on flexible substrate. Solid-State Electronics, 2012, 10.1016/j.sse.2012.06.010. emse-00767177

### HAL Id: emse-00767177 https://hal-emse.ccsd.cnrs.fr/emse-00767177

Submitted on 19 Dec 2012

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> layer used as solid electrolyte in Conductive-Bridge memory devices fabricated on flexible substrate

D. Deleruyelle, <sup>a,\*</sup> M. Putero, <sup>a</sup> T. Ouled-Khachroum, <sup>a</sup> M. Bocquet, <sup>a</sup> M.-V. Coulet, <sup>a</sup> X. Boddaert, <sup>b</sup> C. Calmes, <sup>b</sup> and C. Muller<sup>a</sup>

<sup>a</sup> Im2np, Institut Matériaux Microélectronique Nanosciences de Provence, UMR CNRS 7334, Aix-Marseille Université, Av. Escadrille Normandie Niemen, 13397 Marseille Cedex 20, France

<sup>b</sup> Ecole Nationale Supérieure des Mines de Saint Etienne, Centre de Microélectronique de Provence Georges Charpak, 880 route de Mimet, 13120 Gardanne, Cedex, France

#### **Abstract**

This paper shows that the well-know chalcogenide Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) in its amorphous state may be advantageously used as solid electrolyte material to fabricate Conductive-Bridge Random Access Memory (CBRAM) devices. GST layer was sputtered on preliminary inkjet-printed silver lines acting as active electrode on either silicon or plastic substrates. Whatever the substrate, the resistance switching is unambiguously attested at a nanoscale by means of conductive-atomic force microscopy (C-AFM) using a Pt-Ir coated tip on the GST surface acting as a passive electrode. The resistance change is correlated to the appearance or disappearance of concomitant hillocks and current spots at the surface of the GST layer. This feature is attributed to the formation/dissolution of a silver-rich protrusion beneath the AFM tip during set/reset operation. Beside, this paper constitutes a step toward the elaboration of crossbar memory arrays on flexible substrates since CBRAM operations were demonstrated on W/GST/Ag crossbar memory cells obtained from an heterogeneous fabrication process combining physical deposition and inkjet-printing.

#### 1. Introduction

Resistive Random Access Memories (RRAM) are attracting intensive and increasing research efforts as potential high-density information storage solutions beyond the 15 nm node. [1,3] Various physical phenomena are known to lead to a non-volatile resistive switching effect which are related to different types of RRAM such as Thermo Chemical Memories (TCM) or Valency Change Memories (VCM). [4] The actual driving force for the resistance switching, although electrically induced in all cases, is quite different and depends upon the underlying resistive material. Among the main types of RRAM devices, Electro-Chemical Metallization memory cells (ECM), also referred as Conductive-Bridge Random Access Memories (CBRAM) or Programmable Metallization Cells (PMC)

email: damien.deleruyelle@im2np.fr

Tel: 00 33 491 054 777 Fax: 00 33 491 054 782 [5], are of particular interest due to their low-voltage operations [6,7], their large retention capabilities for more than 10-years [7] and their endurance larger than 10<sup>5</sup> cycles. [8,9] The memory elements simply rely on a solid electrolyte sandwiched between an electrochemically active metallic electrode (i.e. Cu or Ag) and an inert counter-electrode (such as Pt or W). The memory effect is achieved through redox mechanisms enabling the electro-migration of dissolved positives ions (e.g. Ag<sup>+</sup> or Cu<sup>+</sup>) leading to an electro-deposition (set operation) or dissolution (reset operation) of metallic filaments between the two electrodes. Most of the solid electrolyte materials consist in a chalcogenide glass such as GeSe [7], GeS [10], Cu<sub>2</sub>S [11] or oxide glasses such as SiO<sub>2</sub> [12] or Ta<sub>2</sub>O<sub>5</sub>.[13] An extensive summary of the electrolyte/electrode couples employed in CBRAM devices can be found in the recent work published by Valov et al. [5]. Although some works recommended the use of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) layers as a way to improve the electrical behavior of CBRAM devices in terms of power consumption [14], resistance ratio ( $R_{OFF}/R_{ON}$ ) [15] or electrical variability [16], few reports mention its use as a solid electrolyte. In previous works Pandian et al. [17]-[19] showed that crystallized Sb-rich GST layers exhibit Polarity Dependent Resistance (PDR) switching which was attributed to the formation/dissolution of Sb conductive filaments bridging together Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> crystalline grains and both electrodes through the amorphous GST phase. In complement to previously published works, the present paper demonstrates that amorphous Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> layer can also be used as a solid electrolyte in CBRAM devices employing silver as the active electrode. Using an heterogeneous fabrication process combining printed and/or sputtered electrodes and sputtered GST layer, CBRAM memory effect is clearly evidenced in the GST layer either at a nanoscale by conductive atomic force microscopy (C-AFM) or at a micrometric scale on crossbar cells with a W top electrode. In addition, in a context of constant development of new applications lying beside the silicon solid-state devices, memory material stacks were deposited on a flexible plastic substrate in view of future low-voltage embedded applications such as RFID (Radiofrequency Identification) systems.

#### 2. Experimental details

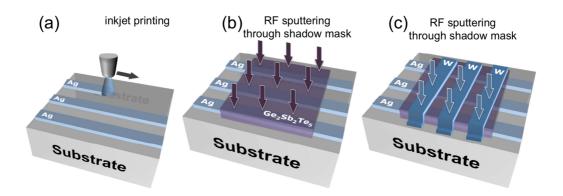

Figure 1 illustrates the main fabrication steps of the samples. The substrates consisted in either Si(100) wafers covered by a 200 nm-thick SiO<sub>2</sub> layer or 120  $\mu$ m-thick polyimide (Kapton® 500-HN) foils. At first, silver lines (350nm-thick, 100  $\mu$ m wide) were deposited by inkjet printing of a commercial silver ink (SunChemical EDM5603) consisting of Ag nanoparticles with a diameter of about 80 nm in a mixture mainly composed of ethanediol and ethanol. The used printing head is a Spectra Galaxy JA 256/30 AA, providing ink drops of 30 pL. A printing resolution of 608 dpi was used. The patterns were printed at 300 mm/sec [Fig. 1(a)]. The samples were then annealed during 30 min at 200 °C in order to eliminate the organic solvent and fa vor the coalescence of the silver nanoparticles to produce conductive lines. The resulting silver lines were then covered by a GST thin film (thickness varying from 20 to 150 nm) deposited by radiofrequency (RF) magnetron sputtering from a high-purity (99.9999%) stoichiometric  $Ge_2Sb_2Te_5$  target through a shadow mask [Fig. 1(b)]. Some of the samples were finally covered by an inert counter top electrode, consisting of W lines (200 nm thick, 100  $\mu$ m wide) deposited by RF-magnetron sputtering through a shadow mask

perpendicularly to silver lines to produce crossbar devices [Fig 1.(c)]. The amorphous state of the GST layer after deposition on  $SiO_2/Si$  substrates was attested by means of x-ray diffraction [20].

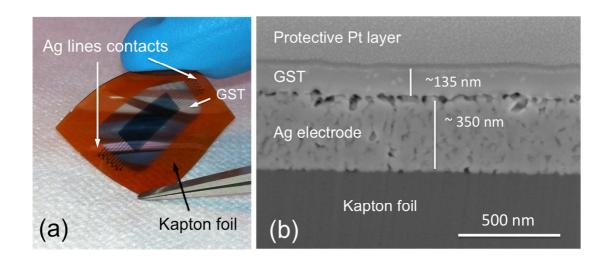

Figure 2(a) shows a picture of a sample taken after the GST deposition (fabrication stage of figure 1(b)). The sample was also characterized by scanning electron microscope (SEM) at the same fabrication stage. The SEM cross-section of Fig. 2(b) shows a 135 nm-thick GST layer deposited on Ag printed lines on a Kapton<sup>®</sup> foil. The micrograph clearly shows a rough interface between the silver lines and the GST layer due to an incomplete coalescence of the Ag nano-particles during post-printing annealing.

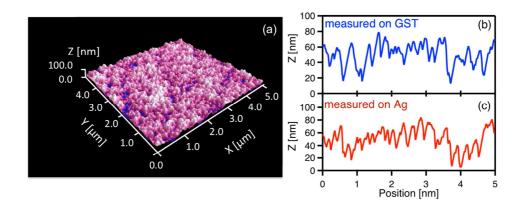

The resistance switching in the memory stack (*i.e.* GST/Ag) was deeply investigated at nanoscales by means of conductive atomic force microscopy (C-AFM) on samples without a top electrode. The measurements were conducted on a Veeco Dimension 3100 with a Nanoscope V controller and platinum-iridium (Pt-Ir) conductive tip enabling the measurement of the local electrical conductivity. Local current-voltage characteristics were measured by applying a voltage bias to the bottom electrode, the AFM tip being grounded. Figure 3(a) shows a 5 µm × 5 µm atomic force microscope (AFM) image obtained in contact mode on a 35 nm-thick GST layer using an insulating silicon nitride tip. The calculated root mean square roughness of this topography map was 14.2 nm which is very close to the one obtained directly on the silver bottom electrode (14.6 nm). This result, in conjunction to the very low roughness measured on the same GST layer deposited on SiO<sub>2</sub>/Si substrates [20], suggests that the roughness of the GST layer originates from the underlying printed silver electrode. This was confirmed by the extraction of cross-section profiles obtained either on the GST layer [Fig. 3(b)] or on the silver electrode [Fig. 3(c)] which exhibited similar roughness profiles.

#### 3. Results and discussion

#### 3.1. Resistive switching at a nanoscale on GST/Ag/SiO<sub>2</sub>/Si stack

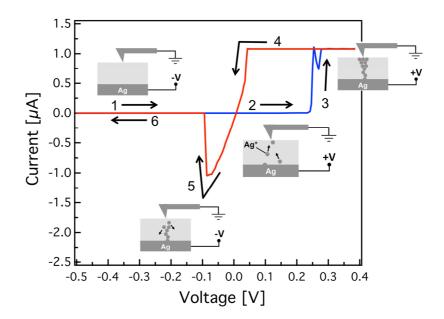

Atomic Force Microscopy (AFM) and its derivative electrical techniques have demonstrated their usefulness in studying resistive switching effects at a nanoscale [21]-[23]. Using a conductive Pt-Ir coated tip, current spectroscopy measurements were performed by means of C-AFM on a 35 nm-thick GST layer deposited on Ag printed lines. In those experimental conditions, the conductive AFM tip acts as a top electrode. While applying voltage sweeps in a range between -1.0 V and +1.0 V to the bottom electrode, the conductive tip being grounded, a neat hysteresis cycle loop is observed on the current-voltage characteristics as shown in Figure 4 where the different steps of the switching process are marked from 1 to 6. More precisely, at a bias voltage of 0.25 V the current level flowing through the tip suddenly overpasses the saturation current of the C-AFM sensor (*i.e.* 1.2  $\mu$ A) (loop parts 1 $\rightarrow$ 3), the sample reaching a low resistance state (LRS). During the reverse sweep the I-V characteristic exhibits an ohmic behavior (4 $\rightarrow$ 5) down to a voltage of -0.1 V. Below this voltage, an abrupt current drop is observed, the measured current going down to the detection limit of the sensor (5 $\rightarrow$ 6) indicating that the sample returned back to a high resistance state (HRS).

This hysteretic I-V characteristic was measured while positioning randomly the tip on the GST layer and was observed in a very reproducible way at different locations on the sample; holding the tip at a fixed position, more than 10 switching cycles could be repeatedly obtained at a scan rate of 1Hz while avoiding thermal drift effects (*i.e.* tip sliding out of the probed region). The shape of the hysteresis loop together with the low voltage operations may be attributed to a conductive-bridge resistive switching effect.[5] This corresponds well to the creation (set) or dissolution (reset) of a metallic conductive filament formed by the electro-deposition of silver-rich aggregates underneath the AFM tip which produces a conductive pathway within the GST layer acting as a solid electrolyte (see inset 3 of Fig. 4). The different stages of the switching characteristic may be detailed as follow:

- From (1→3): starting from the pristine reset state, the set process occurs if a sufficient positive bias voltage (typically 0.25 V) is applied to the active electrode. The overall set process involves (i) the anodic dissolution of Ag creating Ag<sup>+</sup> cations in the GST film, (ii) the electromigration of the Ag<sup>+</sup> cations within the GST layer, (iii) the reduction of Ag<sup>+</sup> to Ag on the vicinity of the inert electrode (*i.e.* conductive AFM tip in present experimental conditions). This process leads to the formation of metallic filaments that bridge both electrodes. At this step, the memory element is in a low resistance state.

- From (4→6): by decreasing the applied voltage, the memory element remains in low resistance state unless a sufficient voltage of opposite polarity is applied with a subsequent electro-dissolution of the metallic filaments that enable switching back the memory element in a high resistance state.

Such low-voltage set and reset operations demonstrated at nanoscale using a conductive AFM tip are very encouraging in terms of scalability of CBRAM technology beyond sub-15 nm technological nodes.

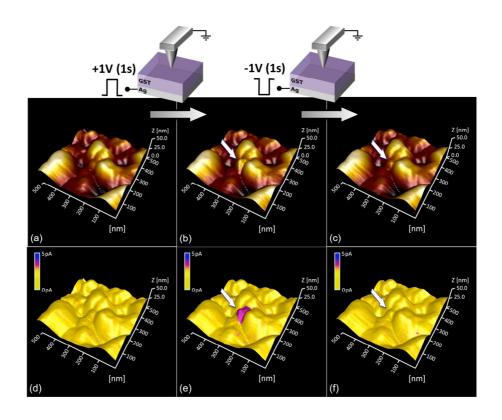

In order to get a deeper understanding on the switching mechanism, a resistive switching cycle was sequentially performed on the GST layer as shown in Figure 5. Simultaneous topography [Figs. 5(a)-(c)] and current images [Figs. 5(d)-(f)] were recorded on a  $0.5 \, \mu m \times 0.5 \, \mu m$  area while applying a 100 mV voltage on the silver bottom electrode. In its initial pristine state (*i.e.* after GST deposition) the explored region does not exhibit any noticeable conductive spot as shown on the current mapping in Fig. 5(d). Upon applying a voltage pulse of +1 V for 1 s in the center of the scanned area (see inset of Fig. 5), a set operation was successfully achieved as demonstrated by the current spot observed within the center of Fig. 5(e). Concomitantly, the corresponding topographic image unambiguously shows the formation of a protrusion underneath the AFM tip upon applying the voltage pulse [Fig. 5(b)]. Interestingly, these correlated structural and electrical modifications are reversible and the hillock could be removed upon the application of a voltage pulse of the opposite polarity, restoring the original topographic and conductance images [Fig. 5(c) and Fig. 5(f)], *i.e.* reset operation. Let us note that similar results were obtained at several locations on several samples, attesting the reproducibility of the resistance switching mechanism.

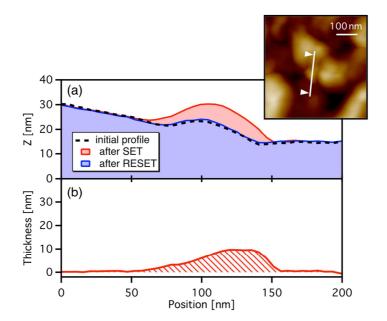

The topographic profiles were extracted across the central region of Figs. 5(a)-(c), and are reported in Fig. 6(a). As already stressed by comparing Figs. 5(a) and 5(c), Fig. 6(a) demonstrates that a complete recovery of the initial morphology is achieved upon the application of a negative bias voltage on the silver electrode. From several sequential switching cycles, the lateral size of the protrusion was measured to be around 100 nm. An average hillock height of 10 nm was extracted by subtracting the initial topographic profile from the one obtained after the set operation [Fig. 6(b)]. Accordingly with the local I-V resistive-switching characteristics, the appearance (resp. disappearance) of the hillock can be attributed to the creation (resp. dissolution) of a silver-rich aggregate underneath the AFM tip during the application of the voltage pulse. Indeed, since there is no blocking top electrode, silver atoms may diffuse out of the chalcogenide layer and then accumulate underneath the AFM tip during the reduction and growth process. Nayak et al. previously reported such an observation during scanning tunneling microscopy (STM) measurements on Ag<sub>2</sub>Sbased atomic switches.[24] The large lateral extension of the conductive protrusion with respect to the contact area between the tip and the sample surface (which can be estimated around few tens of nanometer-square [21]) can be related to the water meniscus formed around the AFM tip placed under atmospheric conditions. [25]. As already reported in a previous work [22], the water meniscus may also act as an electrolyte within which metallic ions may move toward the metallic tip to be electrochemically reduced. Therefore the total width (100 nm) of the electrodeposited protrusion results from interplay between the extension of the field lines generated underneath the AFM tip, which is in the order of the contact area [23], the complex contact between the apex of the tip and the surface roughness and the diameter of the water meniscus formed around the tip which can be, at first order, as large as 2 times the radius of curvature (r<sub>C</sub>) of the tip (r<sub>C</sub>~25 nm in our experiment), depending on atmospheric conditions.

#### 3.2. Resistive switching at a micro-scale induced by nano-lithography

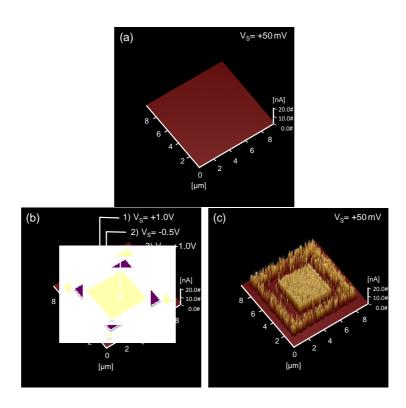

Since the AFM tip consists in a moving top electrode, it can be used to switch a wider area through the application of a negative tip bias (with respect to the grounded bottom electrode) while scanning the surface.[26] Fig. 7(a) shows the current map of a pristine  $10 \,\mu\text{m} \times 10 \,\mu\text{m}$  GST region obtained at a reading sample voltage (V<sub>S</sub>) of +50 mV. The scanned area is initially in a high resistance state since no current spot is detected. By scanning concentric regions at a slow scan speed (0.1  $\,\mu\text{m/s}$ ) and using alternately positive and negative sample bias voltages of +1V/-0.5V [Fig. 7(b)], it was possible to selectively write (*i.e.* set) or erase (*i.e.* reset) square-shaped regions as shown on the C-AFM of Fig. 7(c) recorded using a reading sample voltage value (V<sub>S</sub>= +50 mV). Continuous capture of C-AFM images with the same tip bias showed that the written (*i.e.* bright) regions of Fig. 7(c) persisted over a timescale of half an hour.

#### 3.3. A step toward crossbar memory array on flexible substrate

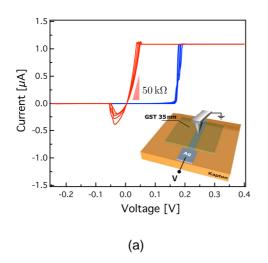

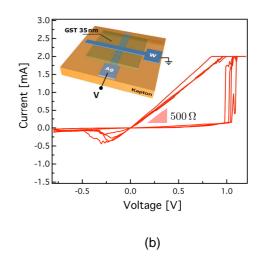

In the same manner, GST/Ag stacks deposited on Kapton® foils were also studied by means of current spectroscopy performed by C-AFM as depicted in the inset of Fig. 8(a). As it can be seen, the shape and orientation of the I-V loop is the same that the one obtained in Fig. 4, this feature indicating that the resistive switching also originates from a conductive-bridge mechanism. Even though set and reset voltages are slightly smaller than those obtained on silicon substrate (cf. Fig. 4), the GST/Ag stack still exhibits an unambiguous memory effect on a plastic substrate. In complement, individual memory elements defined by the 100×100 µm<sup>2</sup> cross-point area between perpendicular Aq (bottom electrode) and W (top electrode) lines were also electrically characterized in ambient conditions using an HP4156C analyzer (Agilent Company). I-V curves were measured from staircase voltage sweeps applied to W top electrode, while the Ag bottom electrode was kept at the ground level. Set and reset operations were achieved upon applying sweeps  $0 \to +1.5 \text{ V} \to -1.5$  $V \rightarrow 0 V$ . The corresponding I-V characteristic is shown on Fig. 8(b). It exhibits a similar memory effect than during C-AFM measurements. From the I-V curves of Fig. 8, the low resistance state value was estimated around 500  $\Omega$  for the crosspoint device, while a value of 50 k $\Omega$  was found in the case of the C-AFM experiment on GST/Ag. The 100 times ratio between both resistance values does not follow the area scaling factor between the active areas involved in the switching process which is in the range of 10<sup>8</sup> considering a 10×10 nm<sup>2</sup> tip-sample contact area. This result illustrates the weak area dependence arising from the filamentary conduction process in CBRAM devices where the current level in the low resistance state is controlled by the number of conductive filaments bridging the top and bottom electrodes rather than by the active area of the device [7]. Finally one can also notice the difference observed in set/reset voltage values between both experiments. In each case a smaller programming (i.e. set or reset) voltage value was obtained in the case of the C-AFM measurements. Although this latter observation needs further clarification, one can invoke the electric field enhancement effect produced in the vicinity of the AFM tip [27] which may improve the migration of metallic ions during set or reset process. In addition, since set and reset processes are electrode-dominated in the case of conductive-bridge devices [5], the difference in set/reset voltages may also originates from the different electronic properties, such as work function of the electrode material, where the ~800 mV difference observed between set voltages almost corresponds to the work function difference between W (4.55 eV) [28] and platinum-iridium (5.3 eV).[29]

To summarize, these above-mentioned results demonstrate the feasibility of crossbar CBRAM memory elements fabricated on a flexible substrate by using heterogeneous elaboration processes combining conventional physical thin film deposition and inkjet-printing. Future measurements, including retention, cycling and robustness against mechanical stress (e.g. bending, stretching...) will be performed in order to assess the performances of such memory cells for future electronic applications on flexible substrates.

#### 4. Conclusions

In summary, this paper demonstrates that amorphous GST thin film may act as a suitable solid electrolyte for conductive-bridge memory devices on flexible substrate. Memory elements were fabricated in combining inkjet-printed silver lines as active electrode and GST layer sputtered either on silicon or plastic substrates. Resistance switching was unambiguously demonstrated at a nanoscale from conductive-AFM measurements using a Pt-Ir coated tip as an inert counterelectrode. Sequential set/reset operations achieved during C-AFM measurements revealed that the resistance switching is accompanied by the reversible formation of a conductive hillock underneath the AFM tip. Based on these results, resistance-switching mechanisms was interpreted in terms of electrodeposition/dissolution of silver-rich conductive filaments within the GST layer. This memory effect was also evidenced at a micrometric-scale by means of nano-lithography as well as on individual crossbar memory elements fabricated on plastic foil and featuring a tungsten top electrode. These promising results constitute a first building block toward the elaboration of conductive-bridge memories on flexible substrates.

#### Acknowledgements

This work has received financial support from the Carnot Institute STAR in the framework of the CORNFlex (Cross-point memory architecture on flexible substrate) project. Thomas Neisius (Université Paul Cezanne and CIM-PACA platform) is gratefully acknowledged for the FIB preparation and cross-section SEM imaging. Inkjet printing was performed using the JETPAC system, an in-line equipment dedicated to printed electronics, actually developed by a research team from the *Centre de Microélectronique de Provence* located in Gardanne (EMSE - France)

#### References

- [1] I.G. Baek, C.J. Park, H. Ju, D. J. Seong, H.S. Ahn, J.H. Kim, M.K. Yang, S.H. Song, E.M. Kim, S.O. Park, C.H. Park, C.W. Song, G.T. Jeong, S. Choi, H.K. Kang, and C. Chung, "Realization of Vertical Resistive Memory (VRRAM) using cost effective 3D Process", *IEDM Tech. Dig.*, pp. 737-740, 2011.

- [2] B. Govoreanu, G.S. Kar, Y-Y. Chen, V. Paraschiv, A. Fantini, I.P. Radu, L. Goux, S. Clima, R. Degraeve, N. Jossart, O. Richard, T. Vandeweyer, K. Seo, P. Hendrickx, G. Pourtois, H. Bender, L. Altimime, D.J. Wouters, J.A. Kittl, and M. Jurczak, "10nmx10nm Hf/HfO<sub>x</sub> Crossbar Resistive RAM with Excellent Performance, Reliability and Low-Energy Operation", *IEDM Tech. Dig.*, pp. 729-732, 2011.

- [3] Z. Wei, T. Takagi, Y. Kanzawa, Y. Katoh, T. Ninomiya, K. Kawai, S. Muraoka, S. Mitani, K. Katayama, S. Fujii, R. Miyanaga, Y. Kawashima, T. Mikawa, K. Shimakawa, and K. Aono, "Demonstration of High-density ReRAM Ensuring 10-year Retention at 85℃ Based on a Newly Developed Reliability Model", *IEDM Tech. Dig.*, pp. 721-724, 2011.

- [4] D. Ielmini, R. Bruchhaus, and R. Waser, "Thermochemical resistive switching: materials, mechanisms, and scaling projections," *Phase Transitions*, vol. 84, no. 7, pp. 570-602, 2011.

- [5] I. Valov, R. Waser, J.R. Jameson, and M.N. Kozicki, "Electrochemical metallization memories-fundamentals, applications, prospects", *Nanotechnology*, vol. 22, no. 25, p. 254003, 2011.

- [6] K. Aratani, K. Ohba, T. Mizuguchi, S. Yasuda, T. Shiimoto, T. Tsushima, T. Sone, K. Endo, A. Kouchiyama, S. Sasaki, A. Maesaka, N. Yamada, and H. Narisawa, "A Novel Resistance Memory with High Scalability and Nanosecond Switching", *IEDM Tech. Dig.*, pp. 783-786, 2007.

- [7] M. Kund, G. Beitel, C-U. Pinnow, T. Rohr, J. Schumann, R. Symanczyk, K-D. Ufert, and G. Müller, "Conductive bridging RAM (CBRAM): an emerging non-volatile memory technology scalable to sub 20nm," *IEDM Tech. Dig.*, pp. 754-757, 2005.

- [8] D. Kamalanathan, A. Akhavan, and M. N. Kozicki, "Low voltage cycling of programmable metallization cell memory devices", *Nanotechnology*, vol. 22, no. 25, p. 254017, 2011.

- [9] Wootae Lee, Jubong Park, Myungwoo Son, Joonmyoung Lee, Seungjae Jung, Seonghyun Kim, Sangsu Park, Jungho Shin, and Hyunsang Hwang, "Excellent State Stability of Cu/SiC/Pt Programmable Metallization Cells for Nonvolatile Memory Applications", *IEEE Electron Dev. Lett.*, vol. 32, no. 5, pp. 680-682, 2011.

- [10] S. Dietrich, M. Angerbauer, M. Ivanov, D. Gogl, H. Hoenigschmid, M. Kund, C. Liaw, M. Markert, R. Symanczyk, L. Altimime, S. Bournat, and G. Mueller, "A nonvolatile 2-Mbit CBRAM memory core featuring advanced read and program control," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 839–845, 2007.

- [11] T. Sakamoto, S. Kaeriyama, H. Sunamura, M. Mizuno, H. Kawaura, T. Hasegawa, K. Terabe, T. Nakayama, and M. Aono, "A nonvolatile programmable solid electrolyte nanometer switch", *ISSCC Tech. Dig.*, pp. 290-529, 2004.

- [12] P. Gonon, C. Vallee, V. Jousseaume, Y. Bernard, C. Mannequin, M. Mougenot, and H. Grampeix, "Comparing the switching characteristics of two resistive RAM technologies: Cu-SiO<sub>2</sub> conductive-bridging-RAMs and HfO<sub>2</sub> Oxide-RAMs", *Proc. IEEE Int. Solid-State and Integrated Circuit Technology*, pp. 1124-1126, 2010.

- [13] T. Sakamoto, N. Banno, N. Iguchi, H. Kawaura, H. Sunamara, S. Fujieda, K. Terabe, T. Hasegawa, and M. Aono, "A Ta<sub>2</sub>O<sub>5</sub> solid-electrolyte switch with improved reliability," *IEEE Symp. VLSI Technology*, pp. 38-39, 2007.

- [14] Wootae Lee Siddik, M. Seungjae Jung Jubong Park Seonghyun Kim Jungho Shin Joonmyoung Lee Sangsu Park Myungwoo Son Hyunsang Hwang, "Effect of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Thermal Barrier on Reset Operations in Filament-Type Resistive Memory", *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1573-1575, 2011.

- [15] Seonghyun Kim, Jubong Park, Seungjae Jung, Wootae Lee, Jiyong Woo, Chunhum Cho, Manzar Siddik, Jungho Shin, Sangsu Park, Byoung Hun Lee, and Hyunsang Hwang, "Excellent resistive switching in nitrogen-doped Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> devices for field-programmable gate array configurations", *Appl. Phys. Lett.*, vol. 99, no. 19, p. 192110, 2011.

- [16] H. Lv, H. Wan, and T. Tang, "Improvement of Resistive Switching Uniformity by Introducing a Thin GST Interface Layer," *IEEE Electron Device Lett.*, vol. 31, no. 9, pp. 978-980, 2010.

- [17] R. Pandian, B.J. Kooi, J.L.M. Oosthoek, P. van den Dool, G. Palasantzas, and A. Pauza, "Polarity-dependent resistance switching in GeSbTe phase-change thin films: The importance of excess Sb in filament formation", *Appl. Phys. Lett.*, vol. 95, no. 25, p. 252109, 2009.

- [18] R. Pandian, B.J. Kooi, G. Palasantzas, J.T.M. De Hosson, and A. Pauza, "Nanoscale Electrolytic Switching in Phase-Change Chalcogenide Films", *Advanced Materials*, vol. 19, no. 24, pp. 4431-4437, 2007.

- [19] R. Pandian, B.J. Kooi, G. Palasantzas, J.T.M. De Hosson, and A. Pauza, "Polarity-dependent reversible resistance switching in Ge–Sb–Te phase-change thin films", *Appl. Phys. Lett.*, vol. 91, no. 15, p. 152103, 2007.

- [20] M. Putero, T. Ouled-Khachroum, M.-V. Coulet, D. Deleruyelle, E. Ziegler, and C. Muller, "Evidence for correlated structural and electrical changes in a Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin film from combined synchrotron X-ray techniques and sheet resistance measurements during in situ thermal annealing," *Journ. of Applied Crystallography*, vol. 44, no. 4, pp. 858-864, 2011.

- [21] D. Deleruyelle, C. Dumas, M. Carmona, C. Muller, S. Spiga, and M. Fanciulli, "Direct Observation at Nanoscale of Resistance Switching in NiO Layers by Conductive-Atomic Force Microscopy", Appl. Phys. Express, vol. 4, no. 5, p. 51101, 2011.

- [22] D. Deleruyelle, C. Muller, J. Amouroux, and R. Mueller, "Electrical nanocharacterization of copper tetracyanoquinodimethane layers dedicated to resistive random access memories", *Appl. Phys. Lett.*, vol. 96, no. 26, p. 263504, 2010.

- [23] M.H. Lee, and C.S. Hwang, "Resistive switching memory: observations with scanning probe microscopy", *Nanoscale*, vol. 3, no. 2, pp. 490-502, 2011.

- [24] A. Nayak, T. Tamura, T. Tsuruoka, K. Terabe, S. Hosaka, T. Hasegawa, M. Aono, "Rate-Limiting Processes Determining the Switching Time in a Ag<sub>2</sub>S Atomic Switch", *J. Phys. Chem. Lett.*, vol. 1, no. 3, pp. 604-608, 2010.

- [25] M. Schenk, and M. Fu, "Direct visualization of the dynamic behavior of a water meniscus by scanning electron microscopy", *J. Appl. Phys.*, vol. 84, no. 9, pp. 4880-4884, 1998.

- [26] K. Kinoshita T. Okutani, H. Tanaka, T. Hinoki, H. Agura, K. Yazawa, K. Ohmi, S. Kishida, "Flexible and transparent ReRAM with GZO memory layer and GZO-electrodes on large PEN sheet", *Solid-State Electronics*, vol. 58, no. 1, pp. 48-53, 2011.

- [27] M.H. Lee, K.M. Kim, S.J. Song, S.H. Rha, J.Y. Seok, J.S. Jung, G.H. Kim, J.H. Yoon, C.S. Hwang, "Surface redox induced bipolar switching of transition metal oxide films examined by scanning probe microscopy." *Applied Physics A*, vol. 102, no. 4, pp.827-834, 2011

- [28] H.B. Michaelson, "The work function of the elements and its periodicity", *J. Appl. Phys.*, vol. 48, pp.4729-4733, 1977

- [29] M. Böhmisch, F. Murmeister, A. Rettenberger, J. Zimmermann, J. Boneberg, P. Leiderer, "Atomic force microscope based Kelvin probe measurements: Applications to an Electrochemical reaction", *J. Phys. Chem. B*, vol. 101, no. 49, pp. 10162-10165, 1997

#### **Figure Caption**

- **Figure 1.** Description of the main fabrication steps of the studied devices. **(a)** Silver electrodes were obtained from printing of silver ink on substrates consisting either in  $SiO_2(200 \text{ nm})/Si$  wafers or plastic foils. **(b)** A GST layer was then deposited by radiofrequency magnetron sputtering on top of the silver lines through a shadow mask. **(c)** Finally W lines were sputtered through a shadow mask to form crossbar memory structures.

- **Figure 2. (a)** Picture of a sample obtained from a plastic substrate consisting of printed silver lines covered by a 135 nm GST layer. The total surface of the GST layer is about 1cm×1.5cm **(b)** Corresponding cross-section SEM view of the sample.

- **Figure 3. (a)**  $5\mu$ m $\times$  $5\mu$ m AFM topographic image obtained on the GST layer. **(b)** Cross-section profile obtained on the GST layer and **(c)** on the silver electrode.

- **Figure 4.** Typical current-voltage characteristic recorded during C-AFM I-V spectroscopy on a 35 nm thick GST layer sputtered on printed Ag lines electrode deposited on a SiO<sub>2</sub>/Si substrate. Schemes referenced from 1 to 6 indicate the orientation of the hysteresis loop and the insets propose a description of the resistive switching phenomenon at its different stages.

- Figure 5. (a)-(c) Topographic and corresponding (d)-(f) current images measured on the top of the GST layer. Each current map was recorded using a sample bias of 100 mV, the tip being grounded. (a) Initial topography and (d) current mappings. (b) and (e) show the morphological and local current modifications induced upon applying a voltage pulse of 1V for 1 s to the bottom electrode, the tip being located in the center of the scanned area. Upon the application of a pulse of reverse polarity, the memory stack turns back in its original configuration as shown in (c) and (f). White arrows indicate the modified region underneath the AFM tip during the application of voltage pulses, as depicted in the insets of the figure.

- **Figure 6.** (color online) **(a)** Topographic profiles extracted from Figs. 5(a)-(c) across the central region as indicated in the inset. Dotted line shows the initial profile obtained from Fig. 5(a). The two other curves were obtained after set (*i.e.* 1V, 1s) and reset (*i.e.* -1V, 1s) operations from Figs. 5(b) and 5(c). **(b)** Extracted height of the protrusion.

- **Figure 7. (a)** Current map of a virgin GST/Ag stack measured at  $V_S$ =+50mV. **(b)** Scheme of alternately biased regions used to write or erase the memory stack. **(c)** Resulting current map measured at  $V_S$ =+50mV.

- **Figure 8.** I-V characteristics measured on a GST/Ag/Kapton<sup>®</sup> stack **(a)** at nanoscales by C-AFM or **(b)** at a micrometric scale on a standard probe station. In this latter case, W top electrode was sputtered perpendicularly to Ag lines to form a crossbar structure.